SignalCore PRESERVING SIGNAL INTEGRITY ТΜ

# Hardware Manual

## SC5307A & SC5308A

6 GHz RF Downconverter

www.signalcore.com

## Table of Contents

| 1 | Gene  | eral Information                                      | 4    |

|---|-------|-------------------------------------------------------|------|

|   | 1.1   | Warranty                                              | 4    |

|   | 1.2   | Copyright & Trademarks                                | 4    |

|   | 1.3   | International Materials Declarations                  | 5    |

|   | 1.4   | CE European Union EMC & Safety Compliance Declaration | 5    |

|   | 1.5   | Warnings Regarding Use of SignalCore Products         | 6    |

| 2 | Physi | cal Description                                       | 7    |

|   | 2.1   | Unpacking                                             | 7    |

|   | 2.2   | Setting Up the Device                                 | 7    |

|   | 2.3   | Front Interface Indicators and Connectors             | 8    |

|   | 2.3.3 | 1 Signal Connections                                  | 9    |

|   | 2.3.2 | 2 Device LED Indicators                               | .10  |

|   | 2.3.3 | 3 Communication and Supply Connection                 | .10  |

|   | 2.3.4 | 4 Mini-USB Connection                                 | .11  |

|   | 2.3.5 | 5 Reset Button (Pin Hole)                             | .12  |

| 3 | Funct | tional Description                                    | .13  |

|   | 3.1   | Overview                                              | .13  |

|   | 3.2   | The Signal Chain                                      | .14  |

|   | 3.2.3 | 1 The RF Input                                        | .14  |

|   | 3.2.2 | 2 The Input Path Switch                               | . 15 |

|   | 3.2.3 | 3 The RF Path                                         | . 15 |

|   | 3.2.4 | 4 The First Mixer and IF1 Path                        | . 15 |

|   | 3.2.  | 5 The Second Mixer and IF2 Path                       | . 17 |

|   | 3.2.6 | 6 External IF2 Input                                  | .17  |

|   | 3.2.7 | 7 The Third mixer and IF3 Path                        | . 18 |

|   | 3.2.8 | 8 Signal Chain Configurations                         | .18  |

|   | 3.3   | The LO Module                                         | . 20 |

|   | 3.3.1 | 1 The Reference Clocks                                | .21  |

|   | 3.3.2 | 2 The First Local Oscillator (LO1)                    | .21  |

|   | 3.3.3 | 3 The Second Local Oscillator (LO2)                   | .22  |

|   | 3.3.4 | 4 The Third Local Oscillator (LO3)                    | . 22 |

|   | 3.4   | The Interface Module                                  | . 22 |

| 4 | Hardware | Registers                                | 23 |

|---|----------|------------------------------------------|----|

|   | 4.1 Con  | figuration Registers                     | 23 |

|   | 4.1.1    | Register 0x01 INITIALIZE                 | 24 |

|   | 4.1.2    | Register 0x02 SYSTEM_ACTIVE              | 25 |

|   | 4.1.3    | Register 0x03 SYNTH_MODE (2 Bytes)       | 25 |

|   | 4.1.4    | Register 0x10 RF_FREQUENCY               | 25 |

|   | 4.1.5    | Register 0x11 IF_FREQUENCY               | 26 |

|   | 4.1.6    | Register 0x14 RF_AMP                     | 26 |

|   | 4.1.7    | Register 0x15 ATTENUATOR                 | 27 |

|   | 4.1.8    | Register 0x16 SIGNAL_PATH                | 27 |

|   | 4.1.9    | Register 0x17 CONFIG_AUTO_GAIN           | 28 |

|   | 4.1.10   | Register 0x18 STORE_DEFAULT_STATE        | 29 |

|   | 4.1.11   | Register 0x19 DEVICE_STANDBY             |    |

|   | 4.1.12   | Register 0x1A REFERENCE_CLOCK            |    |

|   | 4.1.13   | Register 0x1B REFERENCE_DAC              | 31 |

|   | 4.1.14   | Register 0x1C LO1_PATH                   |    |

|   | 4.1.15   | Register 0x1D SYNTH_SELF_CAL             |    |

|   | 4.1.16   | Register 0x1E USER_EEPROM_WRITE          |    |

|   | 4.1.17   | Register 0x1F FREQ_PLAN_PARAM            |    |

|   | 4.2 Que  | ery Registers                            |    |

|   | 4.2.1    | Register 0x30 GET_DEVICE_PARAM           | 34 |

|   | 4.2.2    | Register 0x31 GET_TEMPERATURE            | 34 |

|   | 4.2.3    | Register 0x32 GET_DEVICE_STATUS          |    |

|   | 4.2.4    | Register 0x33 GET_DEVICE_INFO            |    |

|   | 4.2.5    | Register 0x34 CAL_EEPROM_READ            |    |

|   | 4.2.6    | Register 0x35 USER_EEPROM_READ           |    |

|   | 4.2.7    | Register 0x36 SERIAL_OUT_BUFFER          |    |

|   | 4.2.8    | Device Parameters Data and Format        |    |

|   | 4.2.9    | Device Information Parameters and Format |    |

| 5 | Communi  | cation Interfaces                        | 1  |

|   | 5.1 Com  | nmunication Data Format                  | 1  |

|   | 5.2 USB  | Interface                                | 1  |

|   | 5.2.1    | Control Transfer                         | 1  |

| 5.2.     | .2 В      | Bulk Transfer                         |

|----------|-----------|---------------------------------------|

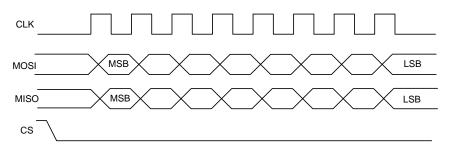

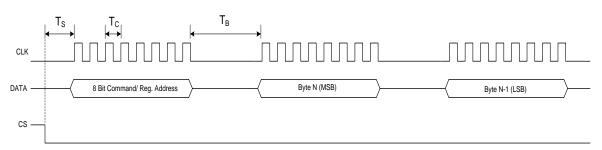

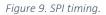

| 5.3      | SPI Int   | erface2                               |

| 5.3.     | .1 V      | Vriting the SPI Bus                   |

| 5.3.     | .2 R      | eading the SPI Bus                    |

| 5.4      | RS232     | Interface                             |

| 5.4.     | .1 V      | Vriting to the Device Via RS2324      |

| 5.4.     | .2 R      | eading from the Device Via RS2325     |

| 5.5      | PXI Ex    | press5                                |

| 5.5.     | .1 S      | etting Up the PCI to Serial Bridge5   |

| 5.5.     | .2 V      | Vriting to the Device6                |

| 5.5.     | .3 R      | leading from the Device6              |

| 6 Calib  | bration . |                                       |

| 6.1      | Calibra   | ation EEPROM Map7                     |

| 6.2      | Absolu    | ute Conversion Gain                   |

| 6.3      | Absolu    | ute Gain of the RF Conversion Path8   |

| 6.4      | Gain T    | hrough the Bypass RF Conversion Path9 |

| 6.4.     | .1 A      | pplying Calibration9                  |

| Revision | Table     |                                       |

## 1 General Information

#### 1.1 Warranty

This product is warranted against defects in materials and workmanship for a period of three years from the date of shipment. SignalCore will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

Before any equipment will be accepted for warranty repair or replacement, a Return Material Authorization (RMA) number must be obtained from a SignalCore customer service representative and clearly marked on the outside of the return package. SignalCore will pay all shipping costs relating to warranty repair or replacement.

SignalCore strives to make the information in this document as accurate as possible. The document has been carefully reviewed for technical and typographic accuracy. If technical or typographical errors exist, SignalCore reserves the right to make changes to subsequent editions of this document without prior notice to possessors of this edition. Please contact SignalCore if errors are suspected. In no event shall SignalCore be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, SIGNALCORE, INCORPORATED MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF SIGNALCORE, INCORPORATED SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. SIGNALCORE, INCORPORATED WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of SignalCore, Incorporated will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against SignalCore, Incorporated must be brought within one year after the cause of action accrues. SignalCore, Incorporated shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow SignalCore, Incorporated's installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### 1.2 Copyright & Trademarks

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of SignalCore, Incorporated.

SignalCore, Incorporated respects the intellectual property rights of others, and we ask those who use our products to do the same. Copyright and other intellectual property laws protect our

products. Use of SignalCore products is restricted to applications that do not infringe on the intellectual property rights of others.

"SignalCore", "signalcore.com", and the phrase "preserving signal integrity" are registered trademarks of SignalCore, Incorporated. Other product and company names mentioned herein are trademarks or trade names of their respective companies.

#### 1.3 International Materials Declarations

SignalCore, Incorporated uses a fully RoHS compliant manufacturing process for our products. Therefore, SignalCore hereby declares that its products do not contain restricted materials as defined by European Union directive 2002/95/EC (EU RoHS) in any amounts higher than limits stated in the directive. This statement assumes reliable information and data provided by our component suppliers and may not have been independently verified through other means. For products sold into China, we also comply with the "Administrative Measure on the Control of Pollution Caused by Electronic Information Products" (China RoHS). In the current stage of this legislation, the content of six hazardous materials must be explicitly declared. Each of those materials, and the categorical amount present in our products, are shown below:

| 鉛<br>Lead<br>(Pb) | 汞<br>Mercury<br>(Hg) | 镉<br>Cadmium<br>(Cd) | 六价铬<br>Hexavalent<br>Chromium<br>(Cr(VI)) | 多溴联苯<br>Polybrominated<br>biphenyls<br>(PBB) | 多溴二苯醚<br>Polybrominated<br>diphenyl ethers<br>(PBDE) |

|-------------------|----------------------|----------------------|-------------------------------------------|----------------------------------------------|------------------------------------------------------|

| $\checkmark$      | ✓                    | √                    | $\checkmark$                              | $\checkmark$                                 | $\checkmark$                                         |

A  $\checkmark$  indicates that the hazardous substance contained in all of the homogeneous materials for this product is below the limit requirement in SJ/T11363-2006. An X indicates that the particular hazardous substance contained in at least one of the homogeneous materials used for this product is above the limit requirement in SJ/T11363-2006.

#### 1.4 CE European Union EMC & Safety Compliance Declaration

The European Conformity (CE) marking is affixed to products with input of 50 - 1,000 Vac or 75 - 1,500 Vdc and/or for products which may cause or be affected by electromagnetic disturbance. The CE marking symbolizes conformity of the product with the applicable requirements. CE compliance is a manufacturer's self-declaration allowing products to circulate freely within the European Union (EU). SignalCore products meet the essential requirements of Directives 2004/108/EC (EMC) and 2006/95/EC (product safety) and comply with the relevant standards. Standards for Measurement, Control and Laboratory Equipment include EN 61326 and EN 55011 for EMC, and EN 61010-1 for product safety.

#### 1.5 Warnings Regarding Use of SignalCore Products

- (1) PRODUCTS FOR SALE BY SIGNALCORE, INCORPORATED ARE NOT DESIGNED WITH COMPONENTS NOR TESTED FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

- (2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE SOLELY RELIANT UPON ANY ONE COMPONENT DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM SIGNALCORE'S TESTING PLATFORMS, AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE SIGNALCORE PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY SIGNALCORE, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF SIGNALCORE PRODUCTS WHENEVER SIGNALCORE PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

## 2 Physical Description

#### 2.1 Unpacking

All SignalCore products ship in antistatic packaging (bags) to prevent damage from electrostatic discharge (ESD). Under certain conditions, an ESD event can instantly and permanently damage several of the components found in SignalCore products. Therefore, to avoid damage when handling any SignalCore hardware, you must take the following precautions:

- 1. Ground yourself using a grounding strap or by touching a grounded metal object.

- 2. Touch the antistatic bag to a grounded metal object before removing the hardware from its packaging.

- 3. **NEVER touch exposed signal pins.** Due to the inherent performance degradation caused by ESD protection circuits in the RF path, the device has minimal ESD protection against direct injection of ESD into the RF signal pins.

- 4. When not in use, store all SignalCore products in their original antistatic bags.

Remove the product from its packaging and inspect it for loose components or any signs of damage. Notify SignalCore immediately if the product appears damaged in any way.

#### 2.2 Setting Up the Device

Integration of the SC5307A and SC5308A modules requires attention to maintain effective cooling. Inadequate cooling can cause the temperature inside the RF housing to rise above the maximum for this product, leading to improper performance, reduction of product lifespan, or complete product failure. SignalCore suggests providing moderate airflow across the RF housing. If active cooling is not an option, use thermal interface materials to bond the RF housing to a larger heatsinking surface (i.e. a system enclosure). As each device's integrated system configuration is unique, detailed cooling options cannot be provided.

A cooling plan is sufficient when the SC5307A and SC5308A on-board temperature sensors indicate a rise of no more than 20°C above ambient temperature under normal operating conditions.

2.3 Front Interface Indicators and Connectors

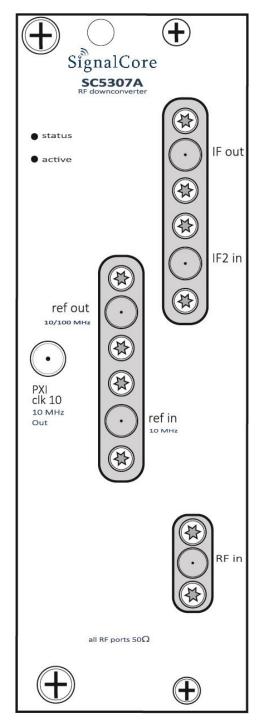

The SC5307A is a PXIe-based RF downconverter with all user I/O located on the front face of the module as shown below:

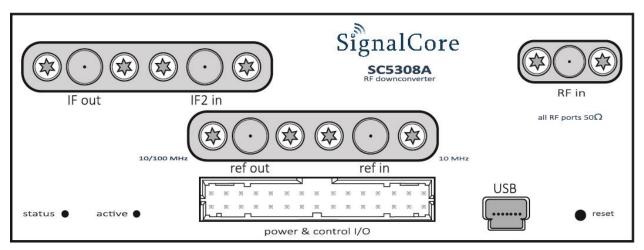

The SC5308A is a serial controlled core module with front face connections shown below:

#### 2.3.1 Signal Connections

All signal connections (ports) on the device are female SMA-type. Exercise caution when fastening cables to the signal connections. Over-tightening any connection can cause permanent damage to the device.

The condition of your system signal connections can significantly affect measurement accuracy and repeatability. Connections that are improperly mated, dirty, damaged, or worn can degrade measurement performance. Clean out any loose, dry debris from connectors with clean, low-pressure air (available in spray cans from office supply stores).

If deeper cleaning is necessary, use lint-free swabs and isopropyl alcohol to gently clean inside the connector barrel and the external threads. Do not mate connectors until the alcohol has completely evaporated. Excess liquid alcohol trapped inside the connector may degrade measurement performance until fully evaporated (this may take several days).

Tighten all SMA connections with 3 in-lb min to 5 in-lb max (56 N-cm max)

- **RF In** This is the RF input port to the device with nominal impedance of 50  $\Omega$ . Its maximum input power is +27 dBm.

- **IF2 In** This is the input to the second IF stage of the converter. Its nominal input frequency is 1250 MHz.

- **IF Out** This is the IF output of the device with nominal impedance of 50  $\Omega$ .

- Ref InThis is the 10 MHz referce input to the device, enabling the device to phase<br/>lock its internal clocks to an external reference source. This nominally 50  $\Omega$  port<br/>is AC coupled. Maximum rated input power is +10 dBm.

**Ref Out** This is the output reference port of the device, allowing for the export of its internal reference clocks. The reference frequency is selectable between 10 MHz or 100 MHz. Typical power level is 3 dBm.

#### 2.3.2 Device LED Indicators

These are LED indicator lights for the device, and their functions are listed in *Table 1* and *Table 2*.

Table 1. Status LED Indicator

| LED Color | Description                                                                 |

|-----------|-----------------------------------------------------------------------------|

| Green     | The device is functioning properly in the state that it is programmed for.  |

| Amber     | Indicates that all functions are on standby mode.                           |

| Red       | Indicates that one or more local oscillators are not functioning correctly. |

| Off       | No supply or supply error.                                                  |

Table 2. Active Indicator

| LED Color | Description                                         |

|-----------|-----------------------------------------------------|

| Green     | An external interface port has accessed the device. |

| Red       | Input supply voltage exceeded.                      |

| Off       | No current interface access.                        |

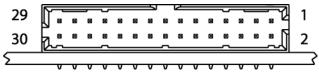

#### 2.3.3 Communication and Supply Connection

Figure 1. Power and Digital IO Connector

Power and communication to the SC5308A is provided through a Molex **Milli-Grid<sup>M</sup>** 2.00mm pitch, 30 position, male header connector. Its part number is 87833-3020. A suggested receptacle female connector is the crimp terminal type 51110-3051 or ribbon type 87568-3093 from Molex. The pin definitions of this I/O connector are listed in *Table 3*.

Pinouts are different for different SignalCore products with the same connector type. Please ensure that mating connectors and cables are wired correctly before connection.

Table 3. Interface connector pin out description

| PIN # | Description     |

|-------|-----------------|

|       | 12V Supply Rail |

| 2,4,6,8,10,12,16,20,24,28 | GND                                          |

|---------------------------|----------------------------------------------|

| 9,11,13,14,15             | Reserved, Do Not Connect                     |

| 17,18                     | Reserved, pull high to 3.3V or DNC           |

| 19                        | Reset, System reset, logic 0 to reset device |

| 21                        | Device Active, accessed                      |

| 22                        | PLL status                                   |

| 23                        | RS232 Baud Rate / SPI Mode Select            |

| 25                        | $\overline{\text{CS}}$ Device select for SPI |

| 26                        | SPI Clock                                    |

| 27                        | TX/MOSI. TX (DTE) for RS232 or MOSI for SPI  |

| 29                        | RX/MOSE. RX (DTE) for RS232 or MISO for SPI  |

| 30                        | SRDY. This pin is serial ready for SPI       |

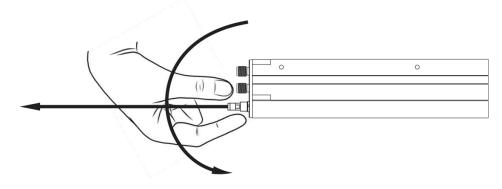

Figure 2. Proper Removal of Latching-Style Ribbon Cable Connectors

#### 2.3.4 Mini-USB Connection

This is a mini-USB Type B connector for USB communication with the device using the standard USB 2.0 protocol (full speed) found on most host computers. The pinout of this connector, viewed from the front, is shown in the following table.

| PIN # | USB Function | Description       |

|-------|--------------|-------------------|

| 1     | VBUS         | Vcc (+5 Volts)    |

| 2     | D-           | Serial Data (neg) |

| 3     | D+           | Serial Data (pos) |

| 4     | ID           | Not Used          |

| PIN # | USB Function | Description                                  |

|-------|--------------|----------------------------------------------|

| 5     | GND          | Device Ground (also tied to connector shell) |

#### 2.3.5 Reset Button (Pin Hole)

Behind this pin hole is the reset button, which is only available on the SC5308A. Using a pin to lightly depress this momentary-action push button switch will cause a hard reset to the device, putting it back to its default settings. All user settings will be lost. System reset capability can also be accessed through the communication header connector.

## 3 Functional Description

#### 3.1 Overview

The SC5308A uses USB as its primary interface with an optional SPI or RS232 interface. The SC5307A is a PXIe version of the product.

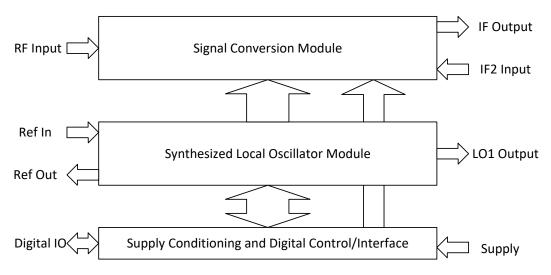

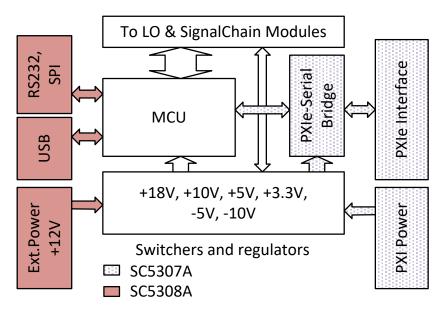

The downconverter assembly consists of three module parts:

- The Signal Conversion Module contains the mixers, filters, signal amplifiers, and attenuators. This module is referred to as the "signal chain".

- The Synthesized Local Oscillator Module that contains the 3 synthesized LO signals and the reference signal circuitry.

- The Power Conditioning and Digital Control Board contains the supply switchers that generate the needs rails for the RF modules and an onboard MCU that provides both the computation engine and interface between the user and the RF modules.

The figure below shows how the modules relate to each other.

Figure 3. Simplified Block Representation of the Downconverter Assembly Module

The downconverter has a maximum of three conversion stages. The first converted intermediate frequency (IF) stage is called IF1, whose signal is converted from the RF input signal. The second converted stage is called IF2, and the third converted stage is IF3. The converted signals in each stage are derived by mixing their respective input signal with their local oscillator (LO) signal. This mixing process results in many products and the desired product at each IF stage is picked out using bandpass filters. Signals that appear inside the passband of the filter will be passed through, while those that are outside the passband are suppressed. Generally, the farther an unwanted signal is away from the filters the better it is suppressed. Unwanted signals that are close to the passband or inside the passband are called spurious signals (or 'spurs' for short). Because of the wide bandwidth of the IF filters there are input RF frequency regions as well as IF output regions where the number and

level of spurs are higher than typical, making those regions unsuitable for high dynamic range applications.

The input tunable range of the downconverter is from  $\approx 100$  kHz to 6 GHz, while the output tunable IF3 range is from  $\approx 10$  MHz to 500 MHz. The RF is tuned using the first local oscillator (LO1), and IF3 is tuned with LO3. IF3 is only tunable when the IF bandwidth is set to 80 MHz or 160 MHz; it is set to a fixed frequency of 1.25 GHz when the converter IF bandwidth is set to 320 MHz.

The frequency accuracy and stability of the device is derived from an onboard Temperature Controlled Crystal Oscillator (TCXO) with accuracy better than 500 ppb. For better accuracy and stability, the downconverter can lock to an external reference of higher precision.

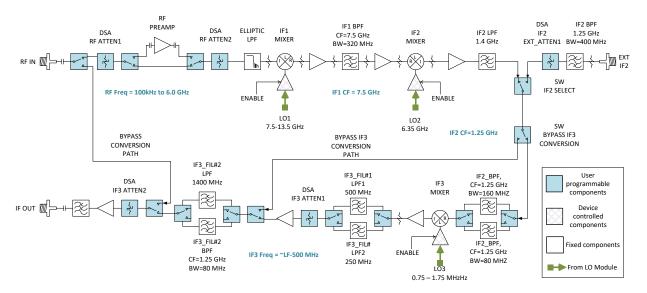

#### 3.2 The Signal Chain

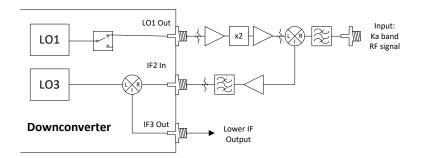

The conversion module contains the mixers, filters, amplifiers, and attenuators used to convert, purify, and maintain the amplitude of the signal, all the way from the input of the device to its output. This cascade of signal conversion and conditioning stages is often referred to as the signal chain, which is shown on the system block drawing in *Figure 4*.

#### 3.2.1 The RF Input

All RF connectors are high quality female stainless steel SMA types rated to 18 GHz of operation. The RF port is AC coupled with a  $0.1 \ uF$  broadband capacitor as indicated in *Figure 4*. The input frequency range at this port is less than 100.0 kHz to greater than 6.0 GHz. The upper limit to which the device tunes to above 6 GHz varies slightly from unit to unit depending on the limits of the oscillator circuitry. The usability of the upper out-of-bounds region depends on the roll-off response of the RF elliptic filter and the IF1 mixer.

Figure 4. Block diagram of the signal conversion module of the downconverter assembly

#### 3.2.2 The Input Path Switch

Immediately following the capacitor is an RF switch to selectively direct the RF signal down two paths:

- 1. The default is the conversion path where the RF signal is converted to a final IF.

- 2. The alternative path is directly to the IF port, bypassing all means of frequency conversion. For lower RF frequency that can be digitized directly by a digitizer at the IF port, this path provides the convenience. Another reason for choosing this path for lower frequencies is that converting low RF to an IF may result in more unwanted spurs at the IF output.

When the conversion path is bypassed, the conversion path and the internal LO are disabled by powering down.

#### 3.2.3 The RF Path

The first device in the RF conversion path is a step attenuator with 1 dB step resolution. This attenuator (RF\_ATTEN) is used to control the signal level at the mixer or at the RF preamplifier. If the RF level at the input of these devices is relatively large with respect to their input compression points, the signal would experience greater nonlinear effects, distorting its waveform, and producing large spurious 3<sup>rd</sup> intermodulation distortion effects.

Following RF\_ATTEN is a switchable RF amplifier that can be switched into the signal path to improve the device sensitivity, effectively lowering the device noise figure. In other words, the effective input noise level of the device is lowered when this amplifier is enabled. Turning on this amplifier is recommended to improve the signal-to-noise dynamic range ( $DR_{SNR}$ ) when expected signal levels are lower than -30 dBm. The typical maximum gain of the downconverter without the amplifier enabled is +30 dB. When the amplifier is enabled, its additional +15 dB will boost the typical maximum gain to +45 dB.

The attenuator (RF\_ATTEN2) following the amplifier switch is used together with RF\_ATTEN1 to control the level at the input of the mixer. Unless the input level is very high, and the attenuation range of RF\_ATTEN1 is exhausted, RF\_ATTEN2 is not commonly used except when the RF amplifier is enabled. RF\_ATTEN1 and RF\_ATTEN2 provide 60 dB of attenuation range, which is enough to keep the device in the linear mode of operation even for signal levels near the maximum recommended value of +27 dBm.

Between RF\_ATTEN2 and the mixer is the RF elliptic low pass filter. This filter cuts off just above 6 GHz and has better than 75 dB of rejection for frequencies above 7.5 GHz. This suppresses back-travel LO leakages to better than -100 dBm (typically -120 dBm) at the input RF port. Another function of this filter is to provide superior suppression of RF image frequencies. The lack of suppression of these RF images could result in mixing with LO1 and appear as spurious components in the IF.

#### 3.2.4 The First Mixer and IF1 Path

The first mixer (IF1 mixer) of the downconverter is very critical as it sets the dynamic ranges of the device for both the signal-to-noise and third order IMD ( $DR_{IMD}$ ) dynamic ranges. The  $DR_{SNR}$  and  $DR_{IMD}$  are directly related to the mixer input compression point (IP1dB) and to the input third-order

intercept point (IIP3). The IIP3 of the mixer is typically better than +18 dBm, and its P1dB is better than 5 dBm. In applications that require better signal linearity, it is recommended that the level at the mixer input is kept at -20 dBm or less. Typically, the IMD is better than -75 dBc for two -20 dBm tones at the mixer. Increasing the level at the mixer improves SNR of the IF output signal at the expense of linearity.

Another important characteristic of the mixer is the LO-IF isolation and LO-RF isolation. The higher the isolation, the lower the leakage LO signal is at the RF and IF ports. The IF1 mixer is driven with a  $\approx$ +20 dBm LO1 signal and the LO-IF isolation is about 45 dB, resulting in a -25 dBm LO1 leakage in the IF1 path. If the RF signal level at the mixer is -20 dBm and the mixer conversion loss is -8 dB, the converted IF1 signal is -28 dBm. For this case, the LO leakage is greater than the converted IF signal. For most of the RF input range, the LO1 leakage is not an issue because the first IF filter (IF1 BPF) will suppress it. Furthermore, when the leakage passes through the IF2 bandpass filters, it will be further suppressed. However, when the downconverter turns to lower frequency, especially when the RF is near the value of the bandwidth of these filters, the LO1 becomes an unwanted spur.

The frequency relationship between the three ports of the mixer is given as:

#### LO = IF + RF

As RF approaches 0 Hz, LO -> IF, resulting in the LO leakage being inside the passband of the filter. The filters are not able to optimally reject leakages inside their passband or within their filter slope. This LO1 leakage will mix with the converted IF1 signals or with LO2 to produce higher order unwanted in-band spurs that could be large enough to affect the recovery of signal data. These intermodulation spurs are usually not so easy to determine and deal with. Having high linearity components helps maintain these spurs at acceptable levels. The linearity in these modules keeps these types of 3<sup>rd</sup> order effects at typically less than -60 dBc. In addition, the LO leakage is a known signal that shows up as the DC value when the final IF spectrum is digitized and processed. For lower RF frequencies it is recommended to switch the RF directly to a digitizer at the IF port instead of putting it through the conversion stages. The user should determine whether the application can tolerate LO leakages, what the effects will be, and decide on the most appropriate route to take.

The first IF (IF1) frequency is centered typically at 7.5 GHz with a minimum bandwidth of 320 MHz. This center frequency may be adjusted programmatically from 7.4 GHz to 7.6 GHz, stepping every 5 MHz. The default center frequency is set at the factory at the time of calibration to compensate for shifts in the IF1 filter response due to fabrication variations. Another advantage of setting the IF frequency higher is to place it closer to the filter slope region, providing better LO1 leakage suppression which is especially beneficial when IF2 is directly routed to the IF port to take advantage of the wider operating bandwidth.

This stage of conversion is an up conversion rather than a down conversion. This broadband architecture simplifies the input RF and IF1 sections to achieve:

1. Superior image rejection without the use of multiple RF bandpass filters.

2. Great RF suppression and isolation in the IF2 passband without multiple IF and LO frequency bands.

The disadvantage of this approach is the requirement of high IF1 and LO1 frequencies which places demanding phase noise requirements on the LO1 synthesizer.

#### 3.2.5 The Second Mixer and IF2 Path

The second IF (IF2) is typically centered at 1.25 GHz and has settable range with 5 MHz steps. The relationship between LO2, IF1, and IF2 is:

$$LO2 = IF1 - IF2$$

IF1 and IF2 are settable with the condition that LO2 must be greater than or equal to 6.25 GHz and less than or equal to 6.45 GHz.

The converted IF2 signal out of the mixer is passed through a 1.5 GHz filter to suppress IF1 and LO1 leakages. The IF2 LPF is not aggressive, so converted LO1 leakages that are close to the IF1 frequency may appear at relatively high values in the IF2 path. After IF2 LPF, the signal has 2 optional paths to take:

- 1. Pass through the selectable bandpass filters BPF1 and BPF2, with frequency bandwidths of 160 MHz and 80 MHz respectively. This signal will then be converted to IF3 via the third IF3 mixer.

- 2. Bypass the third stage conversion and route directly to the output IF3\_FIL#2 selectable filters. The first of these filters is an LPF, and the other is a bandpass filter with 80 MHz wide bandwidth. The broadband LPF will pass greater than 320 MHz of signal bandwidth, however it will also pass LO leakages especially for RF frequencies that are 700 MHz or less. It is HIGHLY RECOMMENDED to use an external 1.25 GHz BPF with an aggressive rejection slope external to the IF output to suppress LO leakages when the device is tuned to lower RF frequencies. The driver amplifier to mixer 3 is disabled when IF3 conversion is bypassed, effectively disabling the mixer conversion process.

If the second IF2 is selected for further down conversion, select the appropriate filter for the desired bandwidth. When the signal bandwidth is not larger than 80 MHz, selecting the 80 MHz filter is always a better option for the following reasons:

- 1. It provides better suppression of LO leakages, especially LO1 when the input RF frequencies are low.

- It provides better backward suppression of LO3, which could mix with LO2 to produce in-band spurs when IF3 is set to a low frequency. It is recommended to use the narrower IF2 filter for IF3 frequencies lower than 100 MHz.

#### 3.2.6 External IF2 Input

The downconverter provides an input to an external IF signal that needs further down conversion to a lower IF signal. The input filter has 400 MHz of bandwidth centered on 1.25 GHz, which is a common IF for any Ka-band and C-band downconverters.

#### 3.2.7 The Third mixer and IF3 Path

The third IF (IF3) is tunable from ±5 MHz to ±500 MHz, as LO3 is tuned from 750 MHz to 1750 MHz in 5 MHz steps. The negative value of IF3 indicates that the spectrum is inverted with respect to the RF input spectrum. When spectral inversion is selected, LO3 tunes below IF2, and it tunes above for no spectral inversion. The 2 filters of the IF3\_FIL#1 bank are there to suppress LO3 and IF2 leakages in the IF3 path. For IF3 frequencies less than 200 MHz, select the 250 MHz LPF2 to provide better suppression of the leakages. The 1500 MHz LPF of IF3\_FIL#2 bank should always be selected to allow the signal to pass through. The BPF of IF3\_FIL#2 bank should only be an option when the IF3 conversion path is bypassed.

Attenuators IF3\_ATTEN1 and IF3\_ATTEN2 are used to set the output amplitude of IF3. Attenuation should be applied to IF3\_ATTEN2 first, and any overflow of more than 30 dB is then applied to IF3\_ATTEN1. However, if better linearity is needed, apply the first 6 dB to IF3\_ATTEN1 and then the rest to IF3\_ATTEN2.

#### 3.2.8 Signal Chain Configurations

Recommended signal chain configurations are provided below for various application scenarios. These are strictly recommendations and not indicative of the downconverter function limitations; users will need to adapt the device to their own applications.

#### 3.2.8.1 Low Input RF

If the RF value is on the order of the bandwidth of the narrowest filter, significant LO leakage may appear at the IF output. Placing an external IF filter will provide further suppression of the leakage that appears outside of the passband. If the external digitizer can handle the RF directly, then the RF signal should be switched to the IF port directly, bypassing conversion.

#### 3.2.8.2 Signals Bypassing the Third IF stage

When IF2 is directed to the final IF port, the bandwidth of the signal can be as high as 320 MHz. The bandwidth is shaped by the IF1 BPF, a 7<sup>th</sup> order filter, which does not have an aggressive attenuation slope so LO leakage starts to appear > 60 dBc when the RF is tuned to less than 650 MHz. The following items are recommended operational settings for the device when IF3 is bypassed.

- Tune RF higher than 650 MHz.

- Use an external 1.25 GHz filter at the IF output to suppress leakages. This may allow tuning to lower RF values.

- If the signal bandwidth is less than 80 MHz, select the BPF in the IF3\_FIL#2 filter bank.

#### 3.2.8.3 Signals Converted Down to the Third IF Stage

Signals will pass through the IF2 bandpass filters, namely the 160 MHz and 80 MHz wide bandpass filters. Selecting the narrower filter improves the leakage spurs and allows for a lower center frequency of the final IF. For example, IF3 could be set to 70 MHz if the 80 MHz filter is selected without the risk of possible increase of in-band spurs arising from LO2 - LO3 intermodulation or having significant LO leakages even when the device is tuned for RF as low as 70 MHz.

Filter bank IF3\_FIL#1 has 2 selectable low pass filters: a 500 MHz and a 250 MHz filter. These filters are there to suppress LO3 leakage, IF2 leakage, and high order intermodulation products that are out of band. Select the 250 MHz filter for IF3 values less than 200 MHz.

#### 3.2.8.4 Dynamic Range Setting

There are 2 sets of digital step attenuators to control the conversion gain of the downconverter. The first set consists of RF\_ATTEN1 and RF\_ATTEN2 and the second set consists of IF3\_ATTEN1 and IF3\_ATTEN2. All attenuators, except for IF3\_ATTEN2, have 30 dB range and 1 dB step. Attenuator IF3\_ATTEN2 has 30 dB range and 0.25 dB step.

To set the downconverter for better sensitivity or better SNR, the gain should be shifted to the RF input path of the device, before the mixer. The RF pre-amplifier should be enabled if necessary and/or RF attenuation reduced. The IF3 attenuator is then used to adjust the final IF output level. The drawback is that the signal level starts off higher as it enters the first mixer as well as the subsequent components. As a result, the apparent linearity of the device is lower.

To set the device for better linearity, the gain should be shifted to the output IF3 path (after the third mixer) and reduced in the RF path. The signal power level at the first mixer should be lower than -20 dB for improved linearity. Since the input signal is low, the relative SNR will be lower. But, as the first mixer and subsequent components experience lower power levels, the apparent linearity of the device is improved.

When the device gain is balanced well, the device can achieve SNR better than 130 dBc/Hz while maintaining IMD3 levels close to 80 dBc. These numbers are representative of converters used in large box high end spectrum analyzers. When the device is optimized for best SNR, typical values better than -150 dBc/Hz can be achieved, and when the device is optimized for sensitivity, the input spectral noise floor is typically lower than -160 dBm/Hz. The flexible use of these attenuators allows the downconverter to achieve better than 190 dB of measurement dynamic range.

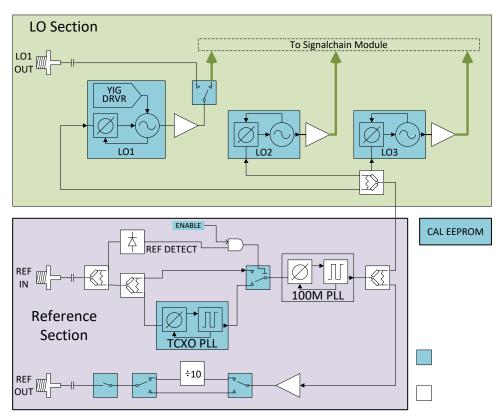

#### 3.3 The LO Module

The local oscillator (LO) module contains three local oscillators, the reference clocks, and the calibration EEPROM as shown in *Figure 5*.

Figure 5. Block diagram of the local oscillator.

#### 3.3.1 The Reference Clocks

The base clock of the downconverter is a 10 MHz Voltage Controlled Temperature Controlled Crystal Oscillator (VCTCXO) with initial accuracy better than 500 ppb once the device has reached a stable temperature. Its initial accuracy is set at the factory via an on-board 14-bit voltage reference DAC. This DAC is accessible for dynamic accuracy calibration. The other reference is a 100 MHz Voltage Controlled Crystal Oscillator (VCXO) which is phase locked to the base reference whenever an external reference source is not used.

When an external reference is selected as the base clock by enabling the device to phase lock to it, the effect only occurs when the presence of this reference is detected. In other words, although the device is programmed to lock externally it will not attempt to do so until the reference signal is detected at the input reference port. Notice, both the reference clocks will attempt to lock to the external source. Having the VCXO lock directly to the external source has the advantage of utilizing the close-in phase noise of the source; it is best to assume that the external source is superior to the internal base. Although the internal VCTCXO is not used when an external reference is selected, it is important to have it remain powered on to maintain its temperature stability. Like the VCXO, it is also phase locked to the external source.

The reference output is derived from the buffered VCXO. When its output is enabled, its frequency can be selected for 10 MHz or 100 MHz. Typically, output power is +3 dBm as its accuracy and stability is that of either the internal VCTCXO or external reference source.

#### 3.3.2 The First Local Oscillator (LO1)

The first local oscillator (LO1) is a YIG based synthesizer tunable between at least 7 GHz and more than 14 GHz typically. Its multiple hybrid PLL approach gives it the advantages of having lower phase noise, very low spurs, and a small frequency step of 1 Hz. This signal drives the first mixer of the signal chain. This signal can also be programmed to route to an external connector to drive an external mixer for frequency conversion outside the limits of the device. For example, its frequency could be doubled externally to drive a Ka band mixer to convert a signal down to an IF of 1.25 GHz, which may be routed into the IF2 input for further down-conversion or conditioning. A possible block presentation of the example is shown below:

The frequency of LO1 is set indirectly by programming the IF1 and RF signal frequencies when it is switched to drive the internal mixer for conversion. When it is programmed to drive externally, its frequency can be set directly by writing the appropriate register.

*Figure 6. Application example of using external LO1 for down conversion of a Ka band signal.*

#### 3.3.3 The Second Local Oscillator (LO2)

The second LO (LO2) tunes between 6.25 GHz and 6.45 GHz in 5 MHz frequency steps and drives the second mixer of the signal chain. Its frequency is indirectly set using IF1 and IF2 values using the following relationship:

$$LO2 = IF1 - IF2$$

The ability to tune LO2 allows for the optimization of IF combinations to move higher order intermodulation products that may form inside the passband to outside the passband.

#### 3.3.4 The Third Local Oscillator (LO3)

The third LO (LO3) frequency is set indirectly with IF2 and IF3 frequency values, and the polarity of the IF3 spectrum is set with respect to the RF. IF3 can be set ideally from DC to 500 MHz. When the IF3 spectrum is set to be non-inverted, LO3 tunes from 1.25 GHz up to 1.75 GHz, otherwise it tunes from 1.25 GHz down to 750 MHz. Caution needs to be taken when tuning to the limits because of larger LO leakages and intermodulation products that could form in-band. For example, when the LO3 is set to 750 MHz in the inverted case, the IF3 low-pass filters are not sufficiently aggressive to provide the suppression that may be needed to keep the leakage to an acceptable level at the IF output port.

#### 3.4 The Interface Module

*Figure 7* shows the power and control interface block for both the SC5307A and SC5308A. All supply rails are produced on board; their voltages are regulated and actively filtered to keep noise to a minimum. Thus, these downconverters are tolerant to "dirty" external power supplies.

Figure 7. Block diagram of the power and interface module

## 4 Hardware Registers

The set of hardware registers of the downconverter may be divided into a configuration set and a query set; the configuration registers are write-only registers to set up the states of the device, while the query registers request the device to prepare and send back data associated with them. The registers are identical for all communication interfaces: PXIe, USB, RS232, and SPI. Data communication to all interfaces are sent in 1 byte wide, that is, data is transferred byte-by-byte. Register data lengths vary in size, and it is important that the correct number of bytes are sent for the corresponding register. Failure to do so may cause communication to lock-up and the device to become unresponsive.

#### 4.1 Configuration Registers

These are write-only registers to configure the device. The registers vary in length to reduce redundant data and improve the communication speed, especially for SPI and RS232 interfaces. Furthermore, it is vitally important that the length of data written to a register is exact because failure to do so will cause the interfaces to misinterpret the incoming data, leaving the device in a stalled state. The total number of bytes is the sum of the register address (1 Byte) and its corresponding data bytes. For example, to set the RF frequency value, eight bytes must be written; the sum of the 1 register byte and 7 data bytes. See the RF\_FREQUENCY register of Table 4. The table provides a summary of the configuration registers, and each register is explained in detail.

| Register Name | Reg Add | Serial<br>Range | Bit 7                                  | Bit 6                                    | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1      | Bit O  |

|---------------|---------|-----------------|----------------------------------------|------------------------------------------|-------------|-------|-------|-------|------------|--------|

| INITIALIZE    | 0x01    | [7:0]           | Set to ze                              | Set to zeros [7:1]                       |             |       |       |       |            |        |

| SYSTEM_ACTIVE | 0x02    | [7:0]           | Set to ze                              | Set to zeros [7:1]                       |             |       |       |       |            |        |

| SYNTH_MODE    | 0x03    | [7:0]           | Set to ze                              | Set to zeros [7:2] Fast-<br>tune Loop Ga |             |       |       |       |            |        |

|               |         | [7:0]           | Frequen                                | cy Word (ł                               | Hz) [7:0]   |       |       |       |            |        |

|               |         | [15:8]          | Frequen                                | cy Word (ł                               | Hz) [15:8]  |       |       |       |            |        |

|               |         | [23:16]         | Frequen                                | Frequency Word (Hz) [23:16]              |             |       |       |       |            |        |

| RF_FREQUENCY  | 0x10    | [31:24]         | Frequen                                | cy Word (H                               | Hz) [31:24] |       |       |       |            |        |

|               |         | [39:32]         | Frequen                                | cy Word (H                               | Hz) [39:32] |       |       |       |            |        |

|               |         | [47:40]         | Frequen                                | cy Word (H                               | Hz) [47:40] |       |       |       |            |        |

|               |         | [55:48]         | Set to ze                              | ros                                      |             |       |       |       |            | LO     |

|               |         | [7:0]           | Frequen                                | cy Word (H                               | Hz) [7:0]   |       |       |       |            |        |

|               |         | [15:8]          | Frequen                                | cy Word (ł                               | Hz) [15:8]  |       |       |       |            |        |

|               |         | [23:16]         | Frequency Word (Hz) [23:16]            |                                          |             |       |       |       |            |        |

| IF_FREQUENCY  | 0x11    | [31:24]         | Frequency Word (Hz) [31:24]            |                                          |             |       |       |       |            |        |

|               |         | [39:32]         | Frequency Word (Hz) [39:32]            |                                          |             |       |       |       |            |        |

|               |         | [47:40]         | Frequency Word (Hz) [47:40]            |                                          |             |       |       |       |            |        |

|               |         | [55:48]         | Set to zeros                           |                                          |             |       |       |       |            |        |

| RF_AMP        | 0x14    | [7:0]           | Set to ze                              |                                          |             |       |       |       |            | Enable |

|               |         | [7:0]           | 0 Attenuator value                     |                                          |             |       |       |       |            |        |

| ATTENUATOR    | 0x15    | [15:8]          | Set to zeros [15:11] Attenuator Number |                                          |             |       |       |       | tor Number |        |

|               |         | [23:16]         | Set to ze                              | ros [23:16                               | ]           |       |       |       |            |        |

#### Table 4. Configuration Registers

| Register Name       | Reg Add | Serial<br>Range | Bit 7                       | Bit 6                | Bit 5                                    | Bit 4        | Bit 3            | Bit 2                 | Bit 1              | Bit O             |  |

|---------------------|---------|-----------------|-----------------------------|----------------------|------------------------------------------|--------------|------------------|-----------------------|--------------------|-------------------|--|

| SIGNAL PATH         | 0x16    | [7:0]           | lf3<br>fil#2<br>select      | lf3 fil#1            | IF2<br>If3 fil#1 select filter<br>select |              | 0                | Bypass<br>IF3<br>conv | Ext. IF2<br>select | Bypass<br>convert |  |

| -                   |         | [15:8]          | Set to ze                   | eros [15:10          | ]                                        |              |                  |                       | Rf amp             | invert            |  |

|                     |         | [23:16]         | Set to ze                   | Set to zeros [23:16] |                                          |              |                  |                       |                    |                   |  |

|                     |         | [7:0]           | Set to ze                   | eros [7:5]           | 5] Linear mode                           |              |                  | Auto<br>ctrl<br>amp   | Load<br>params     | Auto<br>Enable    |  |

| CONFIG_AUTO_GAIN    | 0x17    | [15:8]          | Sign                        | Absolute             | e RF level (                             | 0 - 127) dB  | [6:0]            |                       |                    |                   |  |

|                     |         | [23:16]         | Sign                        | Absolute             | e mixer lev                              | el (0 - 127) | dB [6:0]         |                       |                    |                   |  |

|                     |         | [31:24]         | Sign                        | Absolute             | e IF level (O                            | - 127) dB    | [6:0]            |                       |                    |                   |  |

|                     |         | [39:32]         | Set to zeros                |                      |                                          |              |                  |                       |                    |                   |  |

| STORE_DEFAULT_STATE | 0x18    | [7:0]           | Set all to                  | Set all to zeros     |                                          |              |                  |                       |                    |                   |  |

| DEVICE_STANDBY      | 0x19    | [7:0]           | Set to zeros [7:4]          |                      |                                          |              | Device sections  |                       |                    | Enable            |  |

| REFERENCE_CLOCK     | 0x1A    | [7:0]           | [7:4] set                   | t to zeros           |                                          |              | PXI 10<br>enable | Clk 100<br>enable     | Ref out<br>enable  | Lock ext          |  |

|                     |         | [7:0]           | DAC WO                      | ORD [7:0]            |                                          |              |                  |                       |                    |                   |  |

| REFERENCE_DAC       | Ox1B    | [15:8]          | 0                           | 0 DAC WORD [13:8]    |                                          |              |                  |                       |                    |                   |  |

|                     |         | [23:16]         | Set to ze                   | eros                 |                                          |              |                  |                       |                    |                   |  |

| LO1_PATH            | 0x1C    | [7:0]           | 0                           | 0                    | 0                                        | 0            | 0                | 0                     | 0                  | Ext/Int           |  |

| SYNTH_SELF_CAL      | 0x1D    | [7:0]           | Set all to                  | o zeros              |                                          |              |                  |                       |                    |                   |  |

|                     |         | [7:0]           | BYTE DA                     | ATA [7:0]            | [7:0]                                    |              |                  |                       |                    |                   |  |

| USER_EEPROM_WRITE   | Ox1E    | [15:8]          | ADDRESS [7:0]               |                      |                                          |              |                  |                       |                    |                   |  |

|                     |         | [23:16]         | ADDRES                      |                      |                                          |              |                  |                       |                    |                   |  |

|                     |         | [7:0]           |                             | ncy word (H          |                                          |              |                  |                       |                    |                   |  |

|                     |         | [15:8]          | Frequency word (Hz) [15:8]  |                      |                                          |              |                  |                       |                    |                   |  |

|                     |         | [23:16]         | Frequency word (Hz) [23:16] |                      |                                          |              |                  |                       |                    |                   |  |

| FREQ_PLAN_PARAM     | 0x1F    | [31:24]         |                             | ncy word (H          |                                          |              |                  |                       |                    |                   |  |

|                     |         | [39:32]         |                             | ncy word (H          | ,                                        |              |                  |                       |                    |                   |  |

|                     |         | [47:40]         |                             | ncy word (H          |                                          |              |                  |                       |                    |                   |  |

|                     |         | [55:48]         | Set to ze                   | eros [55:52          | ]                                        |              | PARAM            | [3:0]                 |                    |                   |  |

#### 4.1.1 Register 0x01 INITIALIZE

This register initializes the devices to the default state or reprograms all the device components with the current state parameters. Note, this register does not need to be called in order to program the device.

| Bits  | Туре | Name           | Width | Description                                                                               |

|-------|------|----------------|-------|-------------------------------------------------------------------------------------------|

| [0]   | WO   | Mode           | 1     | 0 = Resets the current state<br>1 = Resets the default to the default or startup<br>state |

| [7:1] | WO   | Unused         | 7     | Set to zeros                                                                              |

| [7:0] | RO   | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232                                           |

#### 4.1.2 Register 0x02 SYSTEM\_ACTIVE

This register turns on or off the active LED indicator on the front connector interface of the device. This register should be called when the device is opened or closed in software.

```

Bytes written 2

Bytes read 1

```

| Bits  | Туре | Name           | Width | Description                                                 |

|-------|------|----------------|-------|-------------------------------------------------------------|

| [0]   | WO   | Mode           | 1     | 0 = Turns off the active LED<br>1 = Turns on the active LED |

| [7:1] | WO   | Unused         | 7     | Set to zeros                                                |

| [7:0] | RO   | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232             |

#### 4.1.3 Register 0x03 SYNTH\_MODE (2 Bytes)

This register configures the PLL loop gain of the local oscillator synthesizers. It also enables or disables faster tuning of the YIG based oscillator of LO1.

Bytes written 2 Bytes read 1

| Bits  | Туре | Name           | Width | Description                                                                                                                   |

|-------|------|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| [1:0] | WO   | Loop Gain      | 2     | 0 = Low loop gain, improves phase noise > 50 kHz<br>1 = Normal loop gain<br>2 = High loop gain, improves phase noise < 50 kHz |

| [2]   | WO   | Fast Tune      | 1     | 0 = Turns fast tune off, default<br>1 = Turns fast tune on, close in phase noise may<br>degrade                               |

| [7:3] | WO   | Unused         | 5     | Set to zeros                                                                                                                  |

| [7:0] | RO   | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232                                                                               |

#### 4.1.4 Register 0x10 RF\_FREQUENCY

This register tunes the device to the input RF frequency.

| Bits    | Туре | Name           | Width | Description                                                                            |

|---------|------|----------------|-------|----------------------------------------------------------------------------------------|

| [47:0]  | W    | Frequency word | 48    | Frequency word in milli-Hz (mHz); mHz used for future compatibility                    |

| [48]    | W    | LO             | 1     | Set to 1 to apply value directly to the first LO. The RF frequency value is unchanged. |

| [55:49] | W    | Unused         | 7     | Set to zeros                                                                           |

| [7:0]   | RO   | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232                                        |

#### 4.1.5 Register 0x11 IF\_FREQUENCY

This register sets the final IF value.

Bytes written 2 Bytes read 1

| Bits    | Туре | Name           | Width | Description                                                         |

|---------|------|----------------|-------|---------------------------------------------------------------------|

| [47:0]  | W    | Frequency word | 48    | Frequency word in milli-Hz (mHz); mHz used for future compatibility |

| [55:48] | W    | Used           | 8     | Set to zeros                                                        |

| [7:0]   | R    | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232                     |

#### 4.1.6 Register 0x14 RF\_AMP

This register enables and disables the RF amplifier.

| Bits  | Туре | Name           | Width | Description                                                   |

|-------|------|----------------|-------|---------------------------------------------------------------|

| [0]   | W    | Frequency word | 1     | 0 = Disables the RF amplifier<br>1 = Enables the RF amplifier |

| [7:1] | W    | Unused         | 7     | Set to zeros                                                  |

| [7:0] | R    | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232               |

#### 4.1.7 Register 0x15 ATTENUATOR

This register sets the value of the device attenuators.

Bytes written 4 Bytes read 1

| Bits    | Туре | Name                     | Width | Description                                                                                                                                             |

|---------|------|--------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]   | W    | Attenuator value         | 8     | In 0.25 dB steps, i.e. LSB = 0.25 dB                                                                                                                    |

| [10:8]  | W    | The target<br>attenuator | 3     | The attenuator number:<br>0 = RF Atten #1<br>1 = RF Atten #2<br>2 = not used<br>3 = External IF input IF2 Atten<br>4 = IF3 Atten #1<br>5 = IF3 Atten #2 |

| [23:11] | W    | Unused                   | 13    | Set to zeros                                                                                                                                            |

| [7:0]   | R    | Read back byte           | 8     | Read 1 byte back is required for PXIe and RS232                                                                                                         |

#### 4.1.8 Register 0x16 SIGNAL\_PATH

This register configures how the signal chain is routed.

| Bit | ts | Туре | Name            | Width | Description                                                                                            |

|-----|----|------|-----------------|-------|--------------------------------------------------------------------------------------------------------|

| [(  | 0] | W    | bypassConverter | 1     | 0 = Normal conversion path<br>1 = Bypasses the conversion, switches RF input<br>directly to IF3 output |

| [2  | 1] | W    | If2ExtSelect    | 1     | 0 = Deselects<br>1 = Selects the IF2 input port                                                        |

| [2  | 2] | W    | bypassIF3Conv   | 1     | 0 = IF2 is converted to IF3<br>1 = IF2 is switched to IF3 output port, bypassing<br>mixer 3 conversion |

| [3  | 3] | W    | If1Filter       | 1     | Not implemented                                                                                        |

| Bits    | Туре | Name           | Width | Description                                                                                                                                               |

|---------|------|----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]     | W    | IF2Filter      | 1     | 0 = Selects the 160 MHz IF2 filter<br>1 = Selects the 80 MHz IF2 filter                                                                                   |

| [6:5]   | W    | IF3Filter1     | 2     | First filter bank of IF3:<br>0 = Selects the 500 MHz LPF<br>1 = Selects the 250 MHz LPF<br>2 = Selects a through path<br>3 = Not implemented              |

| [7]     | W    | lf3Filter2     | 1     | Second filter bank of IF3:<br>0 = 1500 MHz LPF, this should always be selected<br>when IF3 conversion is enabled<br>1 = A narrow 1.25 GHz bandpass filter |

| [8]     | W    | invertSpectrum | 1     | 0 = Not spectral inversion<br>1 = IF3 spectrum inverted w.r.t RF                                                                                          |

| [9]     | W    | rfAmp          | 1     | 0 = Disables RF amp<br>1 = Enables RF amp                                                                                                                 |

| [23:10] | W    | Not used       | 14    | Set to zeros                                                                                                                                              |

| [7:0]   | R    | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232                                                                                                           |

#### 4.1.9 Register 0x17 CONFIG\_AUTO\_GAIN

This register will configure the device to set the attenuator values and control the RF amplifier to keep the device gain close to the desired gain with changes in RF frequency, as computed from its input parameters such as RF input level, mixer level, and IF out level.

```

Bytes written 6

Bytes read 1

```

| Bits | Туре | Name            | Width | Description                                                                                                                                                                                                                               |

|------|------|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0]  | W    | autoGain Enable | 1     | <ul> <li>0 = Attenuator and RF amplifier states are not<br/>manipulated when RF values are changed</li> <li>1 = Computes and applies new sets of attenuator<br/>and amplifier states to the device as frequency is<br/>changed</li> </ul> |

| Bits    | Туре | Name                | Width | Description                                                                                                                                                                                                                   |

|---------|------|---------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]     | W    | loadParams          | 1     | 0 = Not to load new input parameter such as RF<br>level, etc. Will not load any information from bits<br>[47:2]<br>1 = Will load bits [31:2]                                                                                  |

| [2]     | W    | autoCntrlRfAmp      | 1     | 0 = Computation will leave the state of the RF<br>amplifier unchanged<br>1 = Computation will change the state of the RF<br>amplifier to provide the best device<br>configuration to meet the input parameter<br>requirements |

| [4:3]   | W    | linearMode          | 2     | <ul> <li>0 = Best signal-to-noise (SNR), least linear</li> <li>1 = Better SNR, sufficiently linear</li> <li>2 = Better linearity, sufficient SNR</li> <li>3 = Best linearity, least SNR</li> </ul>                            |

| [7:5]   | W    | Unused              | 3     | Set to zeros                                                                                                                                                                                                                  |

| [14:8]  | W    | rfLevel             | 7     | Set the absolute level of the expected RF input level in dB.                                                                                                                                                                  |

| [15]    | W    | rfLevel Sign bit    | 1     | 0 = Positive<br>1 = Negative                                                                                                                                                                                                  |

| [22:16] | W    | mixerLevel          | 7     | Set the absolute level of the expected input mixer level in dB                                                                                                                                                                |

| [23]    | W    | mixerLevel Sign bit | 1     | 0 = Positive<br>1 = Negative                                                                                                                                                                                                  |

| [30:24] | W    | ifLevel             | 7     | Set the absolute level of the expected output IF3 level in dB                                                                                                                                                                 |

| [31]    | W    | ifLevel Sign bit    | 1     | 0 = Positive<br>1 = Negative                                                                                                                                                                                                  |

| [39:32] | W    | Unused              | 8     | Set to zeros                                                                                                                                                                                                                  |

| [7:0]   | R    | Read back byte      | 8     | Read 1 byte back is required for PXIe and RS232                                                                                                                                                                               |

## 4.1.10 Register 0x18 STORE\_DEFAULT\_STATE

This register will store all current settings of the device into EEPROM and will become the default startup setting.

| Bytes written | 2 |

|---------------|---|

| Bytes read    | 1 |

| Bits  | Туре | Name           | Width | Description                                     |  |  |  |

|-------|------|----------------|-------|-------------------------------------------------|--|--|--|

| [7:0] | W    | Unused         | 8     | Set to zeros                                    |  |  |  |

| [7:0] | R    | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232 |  |  |  |

#### 4.1.11 Register 0x19 DEVICE\_STANDBY

This register sets either the entire device or sections of the device into standby mode. Placing a section into standby involves powering down its circuitry. This conserves power and eliminates unwanted LO signals when they are not used.

Bytes written 2 Bytes read 1

| Bits  | Туре | Name           | Width | Description                                                           |

|-------|------|----------------|-------|-----------------------------------------------------------------------|

| [0]   | W    | State          | 1     | 0 = Active<br>1 = Standby enabled                                     |

| [3:1] | W    | Section        | 3     | 0 = Entire device<br>1 = LO1<br>2 = LO2<br>3 = LO3<br>4 = Signalchain |

| [7:4] | W    | Unused         | 4     | Set to zeros                                                          |

| [7:0] | R    | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232                       |

#### 4.1.12 Register 0x1A REFERENCE\_CLOCK

This register configures the reference clock behavior.

| Bits  | Туре | Name           | Width | Description                                                                                           |

|-------|------|----------------|-------|-------------------------------------------------------------------------------------------------------|

| [0]   | W    | LockEnable     | 1     | 0 = Uses internal 10 MHz TCXO<br>1 = Enables frequency locking to external 10 MHz<br>reference source |

| [1]   | W    | RefOutEnable   | 1     | Reference out port enabled                                                                            |

| [2]   | W    | Clk10Enable    | 1     | 0 = 10 MHz output<br>1 = 100 MHz output                                                               |

| [3]   | W    | PXI10Enable    | 1     | Only on SC5307A to enable export of the 10 MHz backplane clock                                        |

| [7:2] | W    | Unused         | 4     | Set to zeros                                                                                          |

| [7:0] | R    | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232                                                       |

#### 4.1.13 Register 0x1B REFERENCE\_DAC

This register makes adjustments to the 10 MHz TCXO accuracy via DAC to its tuning port.

Bytes written 4 Bytes read 1

| Bits    | Туре | Name            | Width | Description                                     |

|---------|------|-----------------|-------|-------------------------------------------------|

| [15:0]  | W    | Tuning DAC word | 16    | DAC WORD                                        |

| [23:16] | W    | Unused          | 8     | Set to zeros                                    |

| [7:0]   | R    | Read back byte  | 8     | Read 1 byte back is required for PXIe and RS232 |

#### 4.1.14 Register 0x1C LO1\_PATH

This register sets the path of LO1; either it drives the internal IF1 mixer or drives out to the LO OUT port connector.

| Bits | Туре | Name | Width | Description                                               |

|------|------|------|-------|-----------------------------------------------------------|

| [0]  | W    | Path | 1     | 0 = LO1 drives IF1 Mixer<br>1 = Drives LO1 to LO OUT port |

| Bits  | Туре | Name           | Width | Description                                     |

|-------|------|----------------|-------|-------------------------------------------------|

| [7:1] | W    | Unused         | 7     | Set to zeros                                    |

| [7:0] | R    | Read back byte | 8     | Read 1 byte back is required for PXIe and RS232 |

#### 4.1.15 Register 0x1D SYNTH\_SELF\_CAL

This register will start the YIG synthesizer calibration. Note that although the calibration procedure takes about 6-8 seconds to complete, the register returns a byte almost immediately.

Bytes written 2 Bytes read 1

| Bits  | Туре | Name           | Width | Description                                     |

|-------|------|----------------|-------|-------------------------------------------------|

| [7:0] | W    | Unused         | 8     | Set to zeros                                    |